# SABLE IO SPECIFICATION

Revision/Update Information: Rev 1.3

-

4000 SYSTEMS AND SERVERS DIGITAL EQUIPMENT CORPORATION MLO5-5/E71 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1990-1994 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation: AlphaServer, DEC LANcontroller, OpenVMS, StorageWorks, VAX, and the DIGITAL logo.

MEMORY CHANNEL is a trademark of Encore Computer Corporation.

**FCC NOTICE:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

## CONTENTS

| Chapter 1 REVISION HISTORY               | 1  |

|------------------------------------------|----|

| 1.1 REV 0.0                              | 1  |

| 1.2 REV 0.1                              | 1  |

| 1.3 REV 1.0                              | 2  |

| 1.4 REV 1.1                              | 2  |

| 1.5 REV 1.2                              | 2  |

| 1.6 REV 1.3                              | 3  |

|                                          | 0  |

| Chapter 2 INTRODUCTION                   | 5  |

| 2.1 Scope                                | 5  |

| 2.2 Requirements                         | 5  |

| 2.2.1 Motherboard Features               | 6  |

| 2.2.2 Standard I/O Module Features       | 6  |

| 2.2.3 Remote I/O Module Features         | 7  |

| 2.2.4 Backplane Features                 | 7  |

| 2.2.4.1 CBUS                             | 7  |

| 2.2.4.2 PCI                              | 7  |

| 2.2.4.3 EISA                             | 7  |

| 2.2.5 Non-Goals                          | 7  |

| 2.3 Block Diagrams                       | 7  |

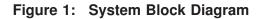

| 2.3.1 System Block Diagram               | 8  |

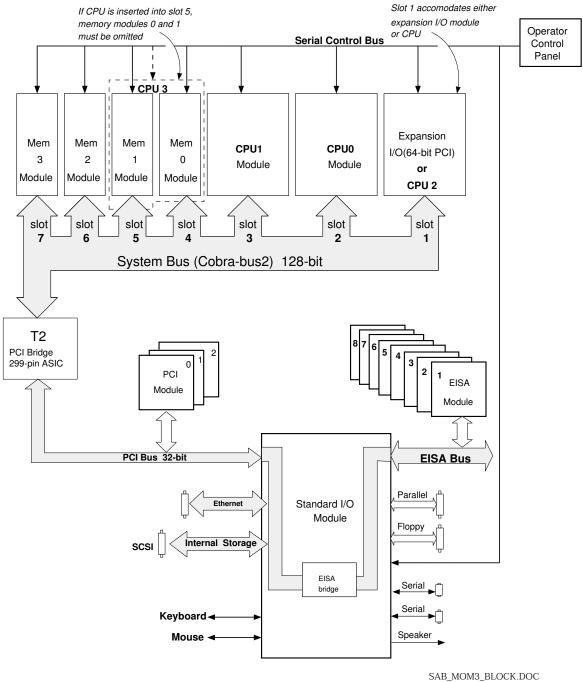

| 2.3.2 Motherboard Physical Placement     | 10 |

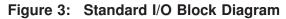

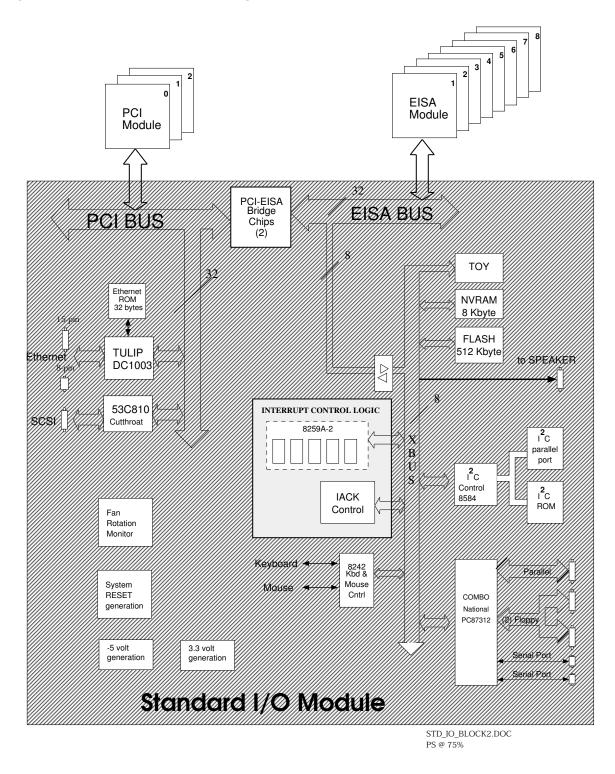

| 2.3.3 Standard I/O Block Diagram         | 11 |

|                                          |    |

| 2.4 Pointers to Related Documentation    | 12 |

| Chapter 3 FUNCTIONALITY                  | 13 |

| 3.1 CBUS                                 | 13 |

| 3.1.1 CBUS Clock Generator/Distributor   | 13 |

| 5.1.1 CBUS Clock Generator/Distributor   | 19 |

| 3.2 PCI                                  | 14 |

| 3.2.1 PCI Clock Generator/Distributor    | 14 |

| 3.2.2 PCI Arbitration                    | 14 |

| 3.2.3 PCI/EISA Interrupts                | 15 |

| 3.2.3.1 Interrupt sequence               | 15 |

| 3.2.3.2 Interrupt priority               | 15 |

| 3.2.3.3 SEOI - Specific End of Interrupt | 16 |

| 3.2.3.4 NMI                              | 17 |

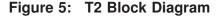

| 3.3 T2 gate array                                        | 17 |

|----------------------------------------------------------|----|

| 3.3.1 T2 Block diagram                                   | 17 |

| 3.3.2 T2 Signals                                         | 19 |

| 3.3.2.1 PCI Signals                                      | 19 |

| 3.3.2.1.1 P_AD[31:0] H - Bidirectional, TTL, BD8TRP, 8ma | 20 |

| 3.3.2.1.2 P_CBE[3:0] L - Bidirectional, TTL, BD8TRP, 8ma | 20 |

| 3.3.2.1.3 P_PAR H - Bidirectional, TTL, BD8TRP, 8ma      | 20 |

| 3.3.2.1.4 P_FRAME L - Bidirectional, TTL, BD8TRP, 8ma    | 20 |

| 3.3.2.1.5 P_IRDY L - Bidirectional, TTL, BD8TRP, 8ma     | 20 |

| 3.3.2.1.6 P_TRDY L - Bidirectional, TTL, BD8TRP, 8ma     | 21 |

| 3.3.2.1.7 P_STOP L - Bidirectional, TTL, BD8TRP, 8ma     | 21 |

| 3.3.2.1.8 P_LOCK L - Input, TTL                          | 21 |

| 3.3.2.1.9 P_DVSEL L - Bidirectional, TTL, BD8TRP, 8ma    | 21 |

| 3.3.2.1.10 P_REQ L - Output, BD8TRP, 8ma                 | 21 |

| 3.3.2.1.11 P_GNT L - Input, TTL                          | 21 |

| 3.3.2.1.12 P_PERR L - Input, TTL                         | 22 |

| 3.3.2.1.13 P_SERR L - Input, TTL                         | 22 |

| 3.3.2.1.14 P_INT H - Input, TTL                          | 22 |

| 3.3.2.1.15 P_RST L - Output, BD4T, 4ma                   | 22 |

| 3.3.2.1.16 P_CLK H - Input, TTL, 50% duty                | 23 |

| 3.3.2.1.17 P_NMI H - Input, TTL                          | 23 |

| 3.3.2.1.18 P_LREAD H - Input, TTL                        | 23 |

| 3.3.2.2 CBUS Signals                                     | 23 |

| 3.3.2.2.1 CAD[127:0] H - Bidirectional, TTL, BD8TRP, 8ma | 23 |

| 3.3.2.2.2 CPAR[3:0] L - Bidirectional, TTL, BD8TRP, 8ma  | 24 |

| 3.3.2.2.3 CXACK L - Bidirectional, TTL, BD8TRP, 8ma      | 24 |

| 3.3.2.2.4 BTPHI1 H, TPHI1 H - Input, TTL, 50% Duty       | 24 |

| 3.3.2.2.5 TPHI1 L - Input, TTL, 50% Duty                 | 24 |

| 3.3.2.2.6 CSHARED L - Output, BD24TRP, 24ma              | 24 |

| 3.3.2.2.7 CUCERR L - Input, TTL                          | 25 |

| 3.3.2.2.8 CA L - Input, TTL                              | 25 |

| 3.3.2.2.9 IOG L - Input, TTL                             | 26 |

| 3.3.2.2.10 CRESET L - Input, TTL                         | 26 |

| 3.3.2.2.11 IOREQ L - Output, BD8T, 8ma                   | 26 |

| 3.3.2.3 IOREQ_L, XIOREQ_L                                | 26 |

| 3.3.2.3.1 CIRQ L - Output, BD8T, 8ma                     | 26 |

| 3.3.2.3.2 CSTALL L - Input, TTL                          | 27 |

| 3.3.2.3.3 C_ERR L - Output, BD24TRP, 24ma                | 27 |

| 3.3.2.3.4 MBA<7:0> H - Bidirectional, TTL, BD2T, 2ma     | 27 |

| 3.3.2.3.5 PARAMOUT - Output, B4, 4ma                     | 28 |

| 3.3.2.3.6 TRIST L - Input, TTL                           | 28 |

| 3.3.3 T2 Functionality                                   | 28 |

| 3.3.3.1 CBUS transactions                                | 28 |

| 3.3.3.2 PCI transactions                                 | 28 |

| 3.3.3.3 Translation Look-aside Buffer (TLB)              | 29 |

| 3.4 Standard I/O Module                                  | 30 |

|                                                          |    |

| Chapter 4 CONTROL STATUS REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 4.1 CBUS CSRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31<br>31                                                                                     |

| 4.2 PCI0 Configuration Registers4.2.1 T24.2.2 TULIP Configuration Registers4.2.3 NCR 53C810 Configuration Registers4.2.4 PCEB Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59<br>60<br>60<br>61<br>63                                                                   |

| 4.3 PCI0 CSRs in PCI0 I/O Sparse Space4.3.1 T24.3.2 TULIP Device Registers4.3.3 NCR 53C810 Device Registers4.3.4 PCEB I/O Registers4.3.5 ESC I/O Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64<br>64<br>65<br>65<br>67<br>68                                                             |

| Chapter 5 ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69                                                                                           |

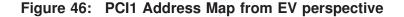

| <ul> <li>5.1 CPU Address Map</li> <li>5.1.1 Memory Space</li> <li>5.1.2 Memory Mapped I/O Space</li> <li>5.1.2 Memory Mapped I/O Space</li> <li>5.1.2.1 CBUS CSRs</li> <li>5.1.2.2 PCI0</li> <li>5.1.2.2.1 PCI0 Sparse Space</li> <li>5.1.2.2.1.1 PCI0 Sparse Memory Space</li> <li>5.1.2.2.1.1 PCI0 Sparse Memory Space - PC Holes Disabled</li> <li>5.1.2.2.1.2 PCI0 Sparse Memory Space - PC Holes Enabled</li> <li>5.1.2.2.1.2 PCI0 Sparse I/O Space</li> <li>5.1.2.2.1.3 Standard I/O Address Mapping</li> <li>5.1.2.2.3 PCI0 Configuration Space</li> <li>5.1.2.4 PCI0 Special Cycles</li> <li>5.1.2.3 PCI1</li> <li>5.1.2.3 PCI1 Configuration Space</li> </ul> | 69<br>71<br>72<br>73<br>74<br>79<br>79<br>80<br>81<br>83<br>83<br>83<br>85<br>89<br>90<br>91 |

| <ul> <li>5.2 PCI Address Map</li> <li>5.2.1 PCI Memory Space and DMA</li> <li>5.2.1.1 DMA Windows</li> <li>5.2.1.1.1 Direct Mapped PCI Address Translation</li> <li>5.2.1.1.2 Scatter/Gather PCI Address Translation</li> <li>5.2.2 EISA Bridge in Sparse Space</li> <li>5.2.2.1 PCI/EISA Bridge</li> </ul>                                                                                                                                                                                                                                                                                                                                                            | 92<br>92<br>95<br>95<br>95<br>99<br>99                                                       |

| Chapter 6 DIAGNOSTIC FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101                                                                                          |

| 6.1 T2 Loopback6.1.1 T2 Loopback Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 101<br>101                                                                                   |

| Chapter 7 ERROR                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 7.1 Errors                                                                                                                                                                                                                                                                                                                                                                                                                                         | 103                                                                       |

| 7.2 MBA Bits                                                                                                                                                                                                                                                                                                                                                                                                                                       | 103                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 200                                                                       |

| Chapter 8 STANDARD AND REMOTE I/O MODULES                                                                                                                                                                                                                                                                                                                                                                                                          | 105                                                                       |

| 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105                                                                       |

| 8.2 Standard IO - PCI to other busses8.2.1 PCI to Ethernet8.2.2 PCI to SCSI8.2.3 PCI to EISA bridge                                                                                                                                                                                                                                                                                                                                                | 105<br>105<br>107<br>107                                                  |

| <ul> <li>8.3 Standard IO - The XBUS</li> <li>8.3.1 XBUS—Memory Devices</li> <li>8.3.1.1 Configuration RAM</li> <li>8.3.1.2 BIOS ROM</li> <li>8.3.2 XBUS—Interrupt Control Logic</li> <li>8.3.2.1 IACK Cycles</li> <li>8.3.2.2 ELCR logic</li> <li>8.3.3 XBUS - Common PC IO Devices</li> <li>8.3.3.1 Keyboard and Mouse Control</li> <li>8.3.3.2 Serial, Parallel, and Floppy Ports</li> <li>8.3.3.4 Speaker</li> </ul>                            | 107<br>108<br>108<br>109<br>110<br>110<br>111<br>111<br>112<br>112<br>112 |

| <ul> <li>8.4 Standard IO - Miscellaneous.</li> <li>8.4.1 I<sup>2</sup>C System Control Bus Devices</li> <li>8.4.1.1 Controller</li> <li>8.4.1.2 I<sup>2</sup>C E<sup>2</sup>PROM</li> <li>8.4.1.3 Expander</li> <li>8.4.2 OCP Interface</li> <li>8.4.3 Reset Circuitry</li> <li>8.4.4 Fan Speed Monitor</li> <li>8.4.5 Voltage Generation</li> <li>8.4.6 Remote System Monitor Option</li> <li>8.4.7 Jumpers.</li> <li>8.4.8 TurboLaser</li> </ul> | 113<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114        |

| 8.5 Remote IO Module                                                                                                                                                                                                                                                                                                                                                                                                                               | 115                                                                       |

| Chapter 9 PHYSICAL CHARACTERISTICS OF I/O MODULES                                                                                                                                                                                                                                                                                                                                                                                                  | 117                                                                       |

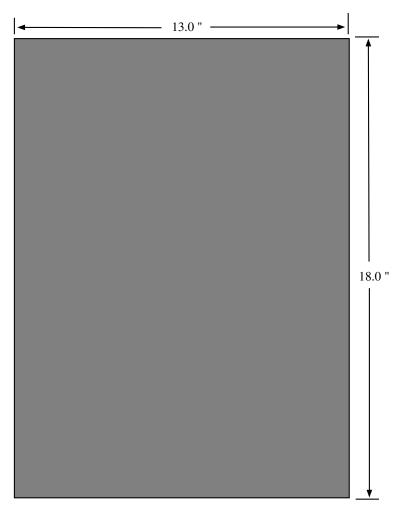

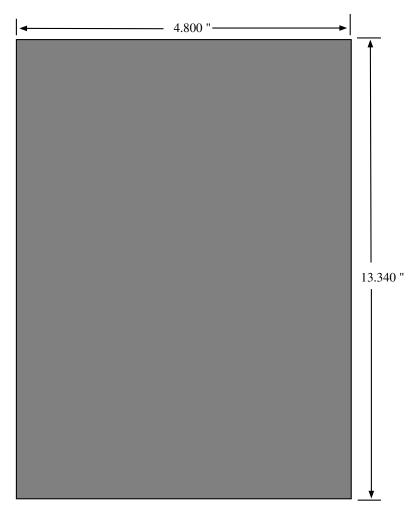

| 9.1 Motherboard       9.1.1 Motherboard Physical Dimensions         9.1.2 Motherboard Layer Construction                                                                                                                                                                                                                                                                                                                                           | 117<br>117<br>119                                                         |

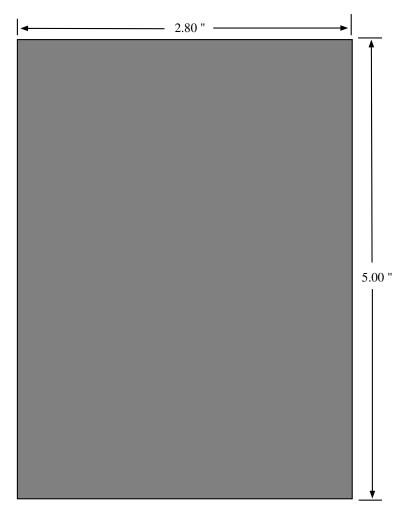

| 9.2 Standard I/O                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 120 \\ 120 \end{array}$                                 |

| 9.2.2 Standard I/O Layer Construction                                                     | 121 |

|-------------------------------------------------------------------------------------------|-----|

| 9.3 Remote I/O                                                                            | 122 |

| Chapter 10 ISSUES                                                                         | 125 |

| 10.1 Pass 2 T2 changes                                                                    |     |

| Appendix A STANDARD I/O ADDRESSING                                                        | 127 |

| Appendix B STANDARD I/O CONNECTORS AND HEADERS                                            | 137 |

| B.1 120 Pin Section of the Gold Fingers                                                   | 137 |

| B.2 240 Pin Section of the Gold Fingers                                                   | 140 |

| B.3 Remote System Monitor Header                                                          | 145 |

| B.4 50 Pin SCSI Header                                                                    |     |

| B.5 60 Pin Header                                                                         |     |

| B.6 34 Pin Floppy Header                                                                  |     |

| B.7 10 Pin OCP Header                                                                     |     |

|                                                                                           |     |

| B.8 8 Pin MJ Connector and 15 Pin Thickwire Connector                                     | 150 |

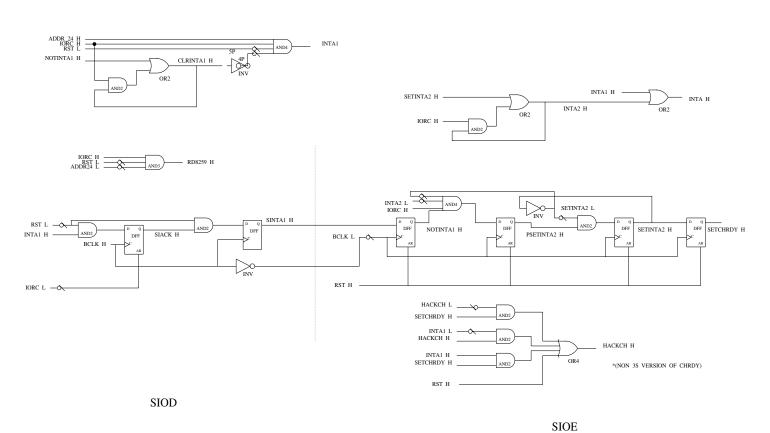

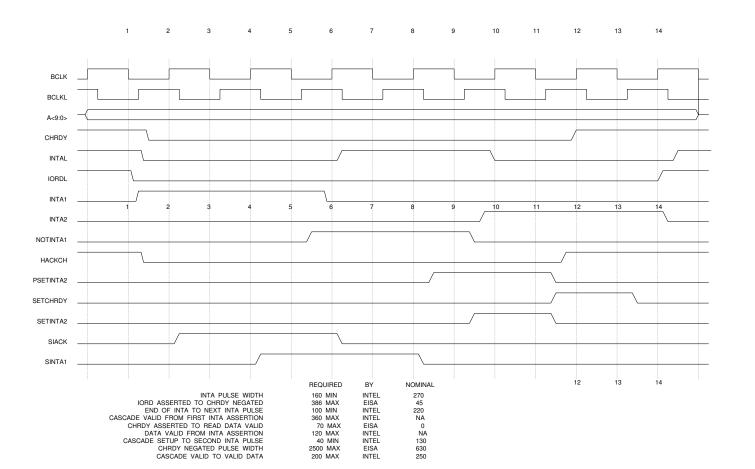

| Appendix C INTERRUPT CONTROL DETAILS                                                      | 153 |

| Appendix D PRELIMINARY POWER CONSUMPTION                                                  | 157 |

| FIGURES                                                                                   |     |

| 1 System Block Diagram                                                                    |     |

| 2 Motherboard Physical Placement                                                          |     |

| 3 Standard I/O Block Diagram                                                              |     |

| 4 Cascaded 8259s Interrupt controller                                                     |     |

| 5 T2 Block Diagram                                                                        |     |

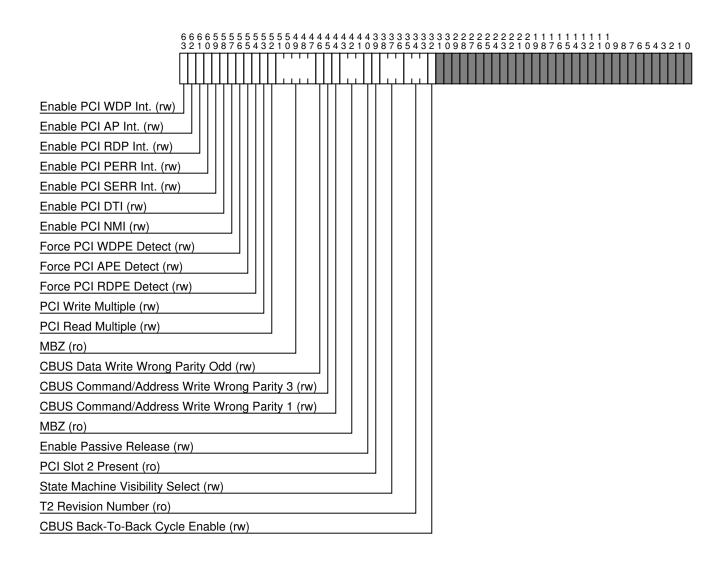

| 6 T2 Signals<br>7 I/O Control/Status Register Low (IOCSRL)                                |     |

| 8 I/O Control/Status Register High (IOCSRI)                                               |     |

| 9 CBUS Error Register 1 (CERR1)                                                           |     |

| 10       CBUS Error Register 2 (CERR2)                                                    |     |

| 11 CBUS Error Register 3 (CERR3)                                                          |     |

| 12 PCI Error Register 1 (PERR1)                                                           |     |

|                                                                                           | 40  |

| 12         FOI Error Register 1 (FERR1)           13         PCI Error Register 2 (PERR2) |     |

| -                                                                                         | 46  |

vii

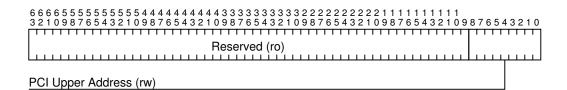

| 16 | High Address Extension Register 2 (HAE0_2)                  | 48  |

|----|-------------------------------------------------------------|-----|

| 17 | High Address Extension Register 3 (HAE0_3)                  | 48  |

| 18 | High Address Extension Register 4 (HAE0_4)                  | 49  |

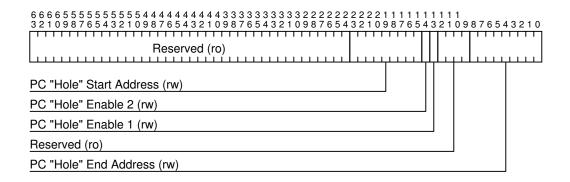

| 19 | PC "Hole" Base Register (HBASE)                             | 49  |

| 20 | Window Base Register 1 (WBASE1)                             | 50  |

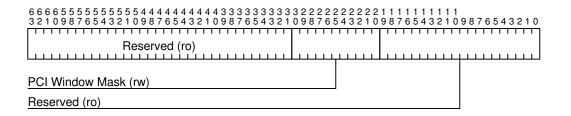

| 21 | Window Mask Register 1 (WMASK1)                             | 51  |

| 22 | Translated Base Register 1 (TBASE1)                         | 51  |

| 23 | Window Base Register 2 (WBASE2)                             | 52  |

| 24 | Window Mask Register 2 (WMASK2)                             | 53  |

| 25 | Translated Base Register 2 (TBASE2)                         | 53  |

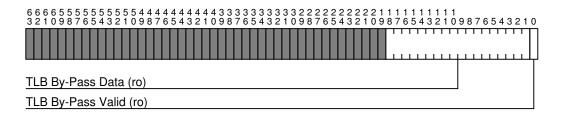

| 26 | TLB By-Pass Register (TLBBR)                                | 54  |

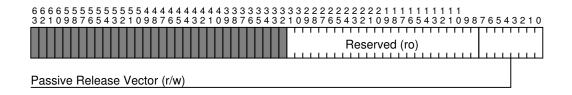

| 27 | IVR Passive Release Register (IVRPR)                        | 54  |

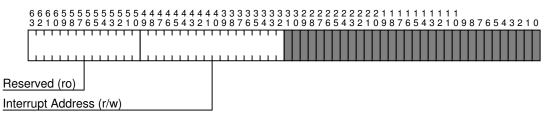

| 28 | IVR Interrupt Address Register (IVIAR)                      | 55  |

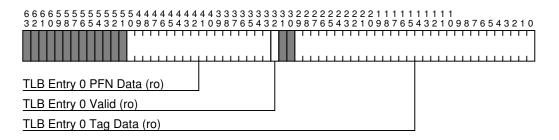

| 29 | TLB Data Register 0 (TDR0)                                  | 55  |

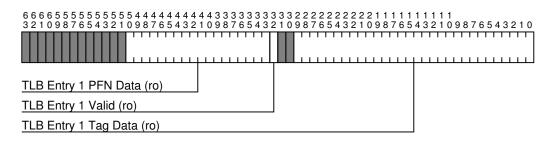

| 30 | TLB Data Register 1 (TDR1)                                  | 56  |

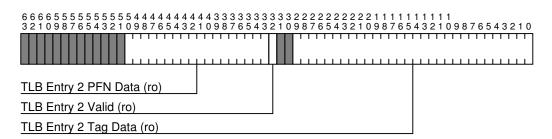

| 31 | TLB Data Register 2 (TDR2)                                  | 56  |

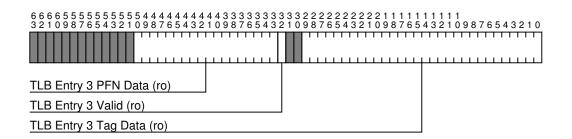

| 32 | TLB Data Register 3 (TDR3)                                  | 57  |

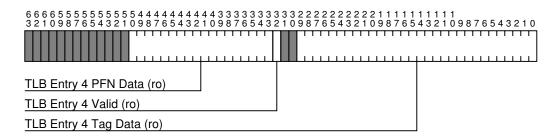

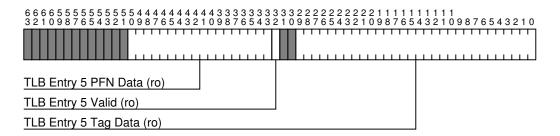

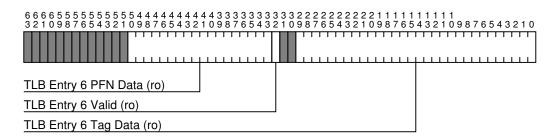

| 33 | TLB Data Register 4 (TDR4)                                  | 57  |

| 34 | TLB Data Register 5 (TDR5)                                  | 58  |

| 35 | TLB Data Register 6 (TDR6)                                  | 58  |

| 36 | TLB Data Register 7 (TDR7)                                  | 59  |

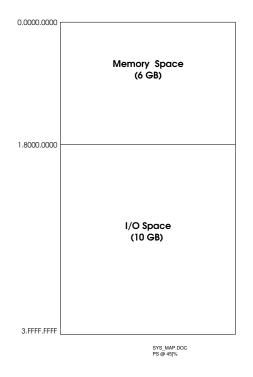

| 37 | System Address Map                                          | 69  |

| 38 | Expanded System Map                                         | 70  |

| 39 | I/O Address Map (10GB)                                      | 72  |

| 40 | CBUS CSRs                                                   | 73  |

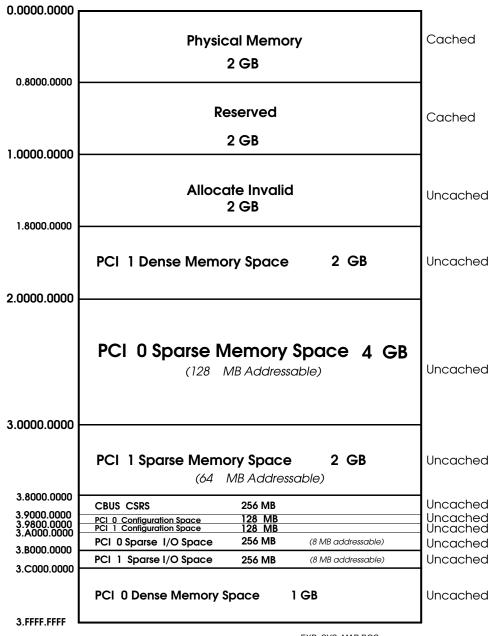

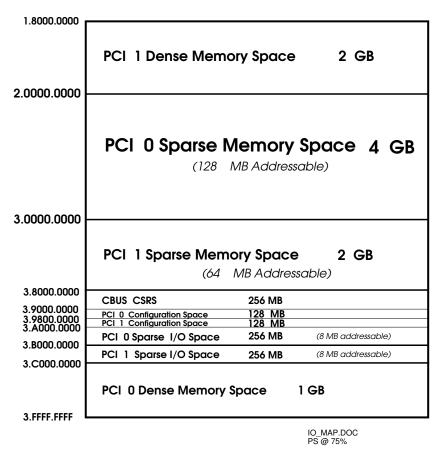

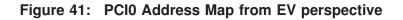

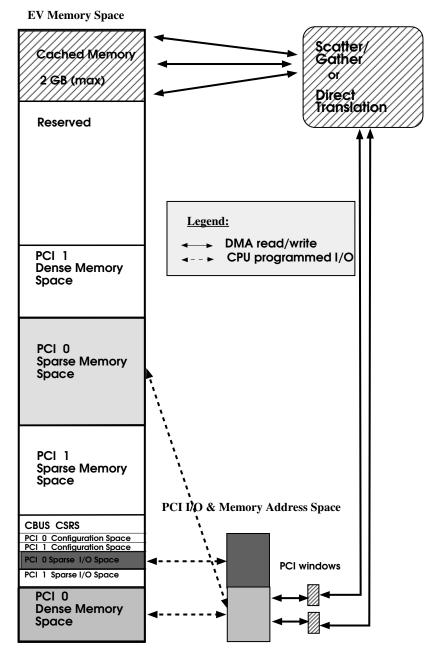

| 41 | PCI0 Address Map from EV perspective                        | 74  |

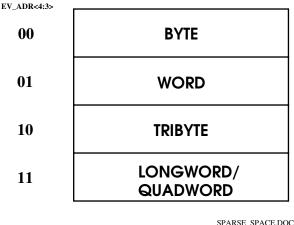

| 42 | Sparse Space Attributes                                     | 75  |

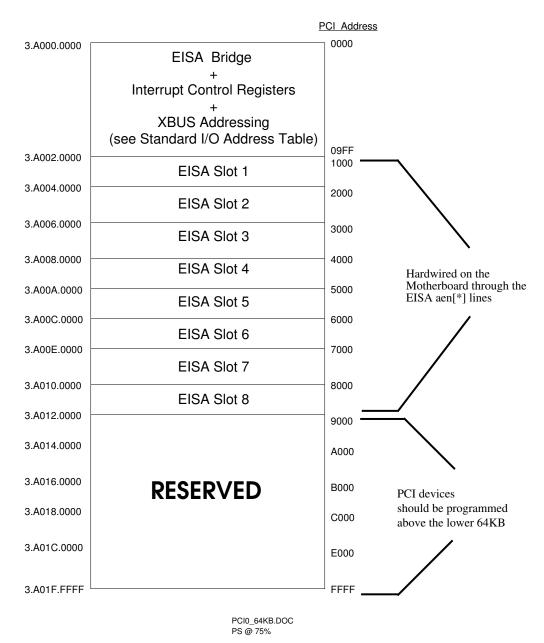

| 43 | Suggested Base Addresses for Lower 64KB PCI0 I/O Space      | 82  |

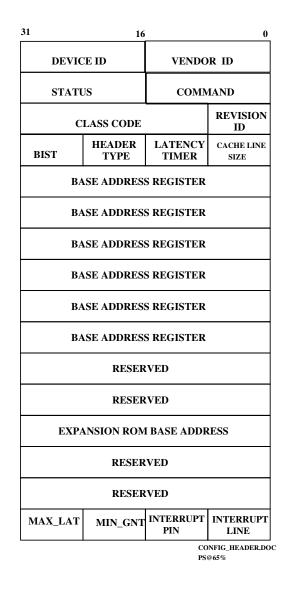

| 44 | PCI Configuration Header                                    | 87  |

| 45 | PCI Special Cycle                                           | 90  |

| 46 | PCI1 Address Map from EV perspective                        | 91  |

| 47 | PTE Format                                                  | 97  |

| 48 | CPU and DMA Reads and Writes                                | 98  |

| 49 | T2 Error Detection                                          | 104 |

| 50 | Standard IO Block Diagram                                   | 106 |

| 51 | Remote IO Connectors, Viewed from the Rear of the Enclosure | 116 |

| 52 | Motherboard Physical Dimensions                             | 118 |

| 53 | Standard I/O Physical Dimensions                            | 120 |

| 54 | Remote I/O Physical Dimensions                              | 122 |

| 55 | PALS SIOD and SIOE, Functional Diagram                      | 154 |

| 56 | PALS SIOD and SIOE, Timing Diagram                          | 155 |

## TABLES

| 1  | T2 Registers                                                                | 32 |

|----|-----------------------------------------------------------------------------|----|

| 2  | I/O Control/Status Register Low Description                                 | 34 |

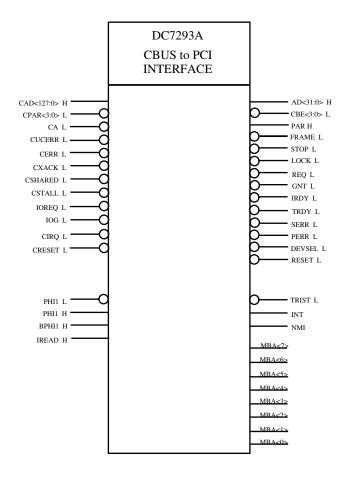

| 3  | I/O Control/Status Register High Description                                | 37 |

| 4  | CBUS Error Register 1 Description                                           | 41 |

| 5  | CBUS Error Register 2 Description                                           | 44 |

| 6  | CBUS Error Register 3 Description                                           | 44 |

| 7  | PCI Error Register 1 Description                                            | 45 |

| 8  |                                                                             | 46 |

| 9  |                                                                             | 47 |

| 10 | High Address Extension Register 1 Description                               | 47 |

| 11 | High Address Extension Register 2 Description                               | 48 |

| 12 | High Address Extension Register 3 Description                               | 48 |

| 13 | High Address Extension Register 4 Description                               | 49 |

| 14 |                                                                             | 49 |

| 15 |                                                                             | 50 |

| 16 |                                                                             | 51 |

| 17 |                                                                             | 52 |

| 18 |                                                                             | 52 |

| 19 |                                                                             | 53 |

| 20 |                                                                             | 53 |

| 21 |                                                                             | 54 |

| 22 |                                                                             | 55 |

| 23 |                                                                             | 55 |

| 24 |                                                                             | 55 |

| 25 |                                                                             | 56 |

| 26 |                                                                             | 57 |

| 27 |                                                                             | 57 |

| 28 |                                                                             | 58 |

| 29 |                                                                             | 58 |

| 30 |                                                                             | 59 |

| 31 |                                                                             | 59 |

| 32 |                                                                             | 59 |

| 33 |                                                                             | 60 |

| 34 |                                                                             | 61 |

| 35 |                                                                             | 63 |

| 36 |                                                                             | 65 |

| 37 | 5                                                                           | 66 |

| 38 | 5                                                                           | 77 |

| 39 |                                                                             | 78 |

| 40 | PCI0 Sparse Memory Space Address Translation for all 128MB - Holes          | -  |

| -  |                                                                             | 79 |

| 41 | PCI0 Sparse Memory Space Address Translation for lower 16MB - Holes enabled | 80 |

| 42 | PCI0 Sparse Memory Space Address Translation for 16MB to $128MB$ -          | 80 |

| 43 |                                                                             | 83 |

| 44 | PCI0 Sparse I/O Space Address Translation for remaining |     |

|----|---------------------------------------------------------|-----|

|    | 64KB-8MB                                                | 83  |

| 45 | Dense Space Address Translation for Reads               | 84  |

| 46 | Dense Space Address Translation for Writes              | 85  |

| 47 | PCI0 IDSEL                                              | 88  |

| 48 | Type 0 Configuration Cycle Generation                   | 88  |

| 49 | Type 1 Configuration Cycle Generation                   | 89  |

| 50 | Direct Mapped PCI Address Translation                   | 95  |

| 51 | Scatter/Gather Map Address Translation for the PTE      | 96  |

| 52 | Motherboard Layup                                       | 119 |

| 53 | Standard I/O Layup                                      | 121 |

| 54 | Remote I/O Layup                                        | 123 |

| 55 | STANDARD I/O ADDRESSING                                 | 127 |

# **CHAPTER 1**

# **REVISION HISTORY**

This chapter contains the current revision history of the Motherboard specification.

#### 1.1 REV 0.0

Initial Draft. Contributors:

- Victoria Triolo

- Rachael Berman

- Tom Hunt

- Fidelma Hayes

- Lee Ridlon

- Paul Rotker

- Andy Russo

- Andy Stewart

- Nick Warchol

- Ralph Ware

- Sue Yuryan

#### 1.2 REV 0.1

Revised from initial review. Contributors:

- Victoria Triolo

- Rachael Berman

- Tom Hunt

- Fidelma Hayes

- Jim Janetos

- Lee Ridlon

- Paul Rotker

- Andy Russo

- Andy Stewart

- Nick Warchol

- Ralph Ware

- Added a 3rd PCI slot

- Changed polarity in the CBUS Mask lines CAD[127:124] and CAD[95:92] in Table 39.

- IOCSR added several bits.

- Added better PCI addressing map.

- Added Standard I/O block diagram.

## 1.3 REV 1.0

Revised from specification review. Contributors:

- Victoria Triolo

- Rachael Berman

- Carl Furbeck

- Tom Hunt

- Fidelma Hayes

- Jim Janetos

- Lee Ridlon

- Paul Rotker

- Andy Russo

- Andy Stewart

- Nick Warchol

- Ralph Ware

## 1.4 REV 1.1

Revised with Standard I/O changes. Contributors:

- Victoria Triolo

- Rachael Berman

- Fidelma Hayes

- Andy Russo

## 1.5 REV 1.2

Revise with review comments from Revision 1.1. Contributors:

- Victoria Triolo

- Rachael Berman

#### 2 DIGITAL EQUIPMENT CORPORATION -

## 1.6 REV 1.3

Revise with review comments from Revision 1.2. Contributors:

- Victoria Triolo

- Andy Russo

- Rachael Berman

# **CHAPTER 2**

# INTRODUCTION

## 2.1 Scope

This document describes the Sable I/O internal subsystem modules. This includes the Motherboard module, which is also the backplane of the Sable system, the Standard I/O module, and the Remote I/O Module. All three modules are required for all Sable systems.

## 2.2 Requirements

The major components of the Sable I/O subsystem are:

- 1. CBUS-PCI bridge, (referred to as the T2 array)

- 2. 3 32-bit PCI slots

- 3. 8 EISA slots

- 4. 1 Ethernet port switchable between 10BaseT and AUI (twisted pair and thickwire)

- 5. 1 fast SCSI port

- 6. PCI-EISA bridge

- 7. Interrupt controller

- 8. Keyboard and mouse controller

- 9. Parallel port

- 10. 2 serial ports

- 11. Floppy controller

- 12. 8 KB NVRAM

- 13. 512 KB Flash ROM

- 14. TOY clock Real time clock

- 15. Speaker

- 16. I<sup>2</sup>C controller and peripheral devices.

These features are implemented across three modules; the Motherboard, the Standard I/O module, and the Remote I/O module.

### 2.2.1 Motherboard Features

The Motherboard is the Sable I/O backplane. It contains System bus (called the CBUS), PCI and EISA slots. The CBUS clocking, PCI clocking, EISA clocking and EISA 14.1818 oscillator are also contained on the Motherboard. There is a 299 pin gate array, called the T2, that is the CBUS to PCI bridge. The Motherboard also has a slot for the standard I/O module. The following is on the Motherboard:

- 1. 7 CBUS slots

- 2. 3 32-bit PCI slots

- 3. 8 EISA slots

- 4. 1 Standard I/O Module slot

- 5. CBUS clock generator/distributor

- 6. PCI clock generator/distributor

- 7. EISA clock distributor

- 8. CBUS-PCI bridge, (referred to as the T2 array)

## 2.2.2 Standard I/O Module Features

The Standard I/O module resides on the internal 32 bit PCI bus. The PCI-EISA bridge resides on this card. The card is standard on all systems. The following is on the Standard I/O module:

1. Digital DC1003 PCI-Ethernet chip (TULIP)

L

- 2. NCR 53C810 PCI-SCSI I/O processor (CUTTHROAT)

- 3. Intel Mercury PCI-EISA bridge chip set (PCEB and the ESC)

- 4. TOY Clock Dallas DS1287A device Real time clock

- 5. Speaker Control

- 6. 8KB NVRAM

- 7. 512 KB Flash ROM

- 8. Keyboard and Mouse Controller Intel/Phoenix 8242

- 9. Combo chip National PC87312

- Parallel port

- Floppy Controller

- 2 Serial ports

- 10.  $I^2C$  Controller, Expander, and ROM

- 11. Interrupt controller for I/O subsystem (PCI and EISA) (8259s)

- 12. Ethernet ROM

- 13. Reset and sysevent logic

- 14. Fan Speed Monitor

- 15. Remote Fault Management Connector

#### 6 DIGITAL EQUIPMENT CORPORATION -

- 16. External PCI sub-arbiter <sup>1</sup>

- 17. 3.3 Volt and -5 Volt generation.

#### 2.2.3 Remote I/O Module Features

The Remote I/O module is mounted inside the back of the system enclosure. It is electrically connected to the system via a 60 pin cable to the Standard I/O Module. It contains the external physical mounting connections for the keyboard and mouse, parallel port, and serial ports. In addition, it contains a jumpered connection for the speaker, which is independently mounted at the back of the enclosure next to the Remote I/O.

#### 2.2.4 Backplane Features

#### 2.2.4.1 CBUS

The CBUS used in Sable is a derivative of the CBUS developed for Cobra. This is the main interconnect between memory, CPUs and the I/O subsystems. There are eight nodes on the CBUS in Sable. Of these, seven nodes are pluggable. The 7 pluggable slots use 240 pin connectors. T2 is the eighth CBUS node. The CBUS is running at 24 ns. (41.67 MHz).

#### 2.2.4.2 PCI

The internal I/O subsystem bus is a 32 bit PCI bus running at 33 MHz. There are three 120 pin PCI connectors for plug-in options. The PCI interfaces to the Ethernet port, SCSI port and the PCI-EISA bridge, all of which reside on the Standard I/O module.

#### 2.2.4.3 EISA

Sable contains 8 EISA slots capable of running at 33 MB/sec. All EISA slots are master capable.

#### 2.2.5 Non-Goals

This specification does not describe optional PCI and EISA modules or the various storage media supported. It also does not describe the External I/O module. For further information, check the Sable System Specification.

## 2.3 Block Diagrams

$<sup>^{1}\,</sup>$  The external PCI sub-arbiter arbitrates between the SCSI controller, and PCI Slot 2.

INTRODUCTION

# 2.3.1 System Block Diagram

See Figure 1.

8 DIGITAL EQUIPMENT CORPORATION -

PS @ 85%

## 2.3.2 Motherboard Physical Placement

MOTHER\_SIMPLE.DOC PS @ 110%

#### 2.3.3 Standard I/O Block Diagram

## 2.4 Pointers to Related Documentation

This document does not replicate information available elsewhere. The following document is useful:

• Sable System Specification

The rest of the Sable specifications are the SABLE\_SPECS notesfile. Contact Subhash Dandage for membership, (PSDVAX::DANDAGE).

Contact Barry Maskas (BAMVAX::MASKAS) for a CBUS specification.

The PCI specification is available through the PCI notesfile. Contact Todd Comins (TECRUS::COMINS) for membership.

There are several chip specifications that are also useful:

- NCR 53C810, PCI-SCSI chip. Contact Bryan Cook, (508-858-0100).

- DC1003, TULIP, For the latest specification, contact Gady Daniely, JEREMY::GADY.

- Intel's 8259A-2, Interrupt controller. See Intel's Peripheral data book.

- Intel's Mercury chip set, PCI-EISA Bridge set. See Intel's <u>82420/82430 PCIset ISA and EISA book</u>.

- Dallas Semiconductor data book for RTC

- NVRAM XICOR's X2864A EEPROM spec

- National's PC87312 spec

- Phillip's I<sup>2</sup>C data books.

- Phoenix MultiKey/42 Technical Reference

# **CHAPTER 3**

# FUNCTIONALITY

## 3.1 CBUS

CBUS is the Sable system bus. It is a 128-bit bus that provides a snooping protocol for write back cache coherent 32-byte block read and write transactions to system memory address space. It supports up to 4 CPU modules, up to 4 memory modules, 1 external I/O module and a CBUS-PCI bridge. There are a total of eight nodes. Sable uses a new version of the CBUS which was originally developed for the Cobra project. The CPUs, memory and I/O subsystems all communicate with each other via the CBUS. The Sable implementation has added a number of features to the original CBUS. These include:

- Direct Mapped Access to I/O devices. Features added to support this are:

- Retry mechanism added to bus

- Longword write masks

- Support for PCI/EISA Locks via priority I/O arbitration mode.

- Expansion to CID filed to allow support for eight CBUS nodes.

- Arbitration to support up to 4 CPU nodes.

- Different CBUS slot definitions:

- 1. Slot #1 External I/O or CPU module 2

- 2. Slot #2 CPU 0

- 3. Slot #3 CPU 1

- 4. Slot #4 Memory 0

- 5. Slot #5 Memory 1 or CPU module 3

- 6. Slot #6 Memory 2

- 7. Slot #7 Memory 3

- Extended addressing to support 40-bit EV addressing.

A diagram of the Motherboard connector layout is shown in Figure 2.

## 3.1.1 CBUS Clock Generator/Distributor

The CBUS clock generator/distributor circuit is located on the Sable Motherboard. This clock is asynchronous to the CPU clock, PCI clock and EISA clocks. The clock period is 24 ns which translates to a clock frequency of 41.67 MHz. The outputs of the clock generator are PHI1, PHI1\_l, PHI3, PHI3\_L. The clock is made up of two phases where phase 3 is 270 degrees behind phase 1. The lock is distributed

as an ECL differential pair on tightly controlled/matched 50 ohm lines. Each CBUS module and the T2 gate array receive their own copy of the CBUS clock. If the oscillator stops, the CBUS reset signal will assert. Refer to the CBUS specification for more details.

### NOTE

The T2 design requires the CBUS clock to always be faster than the PCI clock.

## 3.2 PCI

Sable supports a 32-bit internal PCI bus. Connected to the Sable's PCI bus are the following:

- 1. T2 array

- 2. PCI slot #0

- 3. PCI slot #1

- 4. PCI slot #2

- 5. Tulip chip, PCI-Ethernet bridge

- 6. NCR Cutthroat chip, PCI-SCSI bridge

- 7. Intel Mercury chip set, PCI-EISA bridge

## 3.2.1 PCI Clock Generator/Distributor

The PCI clock generator/distributor is located on the Sable Motherboard. It is a 33 MHz clock. The clock is distributed to the T2, PCI slots and four copies to the Standard I/O module.

#### 3.2.2 PCI Arbitration

The PCEB component, of the Intel PCI to EISA bridge chipset on the Standard I/O module, provides an integrated PCI arbiter. The Sable system has one more PCI device than is supported by this arbiter, so one of the PCEB request and grant pairs is multiplexed between two devices by an external sub-arbiter PAL on the Standard I/O module. The ARB PAL sub-arbitrates between the Cutthroat SCSI controller, and PCI slot 2.

Arbitration is performed with rotating priority. See the databook for the PCEB for more information.

L

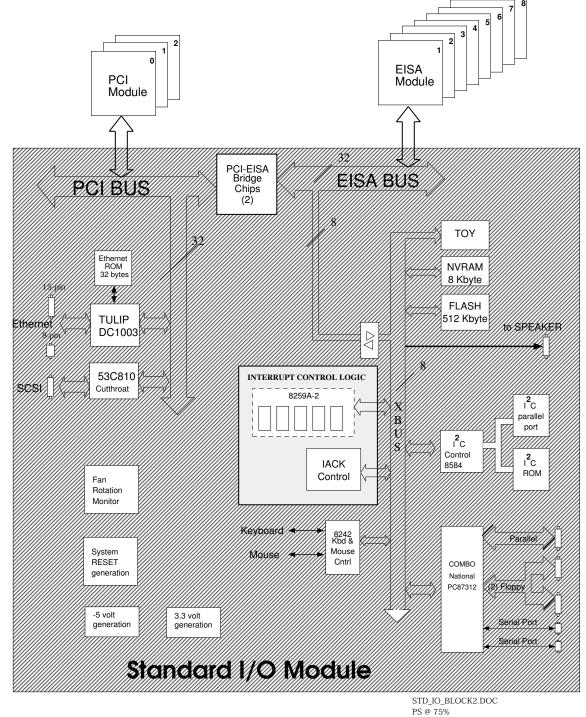

#### 3.2.3 PCI/EISA Interrupts

All Sable PCI, EISA, ISA, and other I/O interrupts will be handled by five Intel 8259As arranged in an 8086 Fully Nested Mode cascade and in a level triggered mode. The hardware is located on the Standard I/O Module. Firmware support will be required for acknowledge and end of interrupt (EOI) handling. There is one master and 4 slave 8259s. See Figure 4 which illustrates the interrupt hierarchy, and Chapter 8, which describes the hardware in more detail.

#### 3.2.3.1 Interrupt sequence

- 1. An EISA, PCI or XBUS device posts an interrupt by asserting its interrupt line to the interrupt control logic.

- 2. The interrupt control logic asserts the INT line to the T2 gate array.

- 3. The T2 asserts the CIRQ<0> L to the CPUs.

- 4. A CPU (called CPUx) performs an I/O read to the IVR register (programmable address).

- 5. The T2 allocates an internal I/O buffer to the first CPU which did the read to the IVR register (CPUx)

- 6. The T2 passes the IVR read to the PCI bus where the interrupt control logic deals with it.

- 7. The T2 de-asserts the CIRQ<0> L and retries CPUx.

- 8. If a different CPU attempts to service the same interrupt as CPUx, it gets a passive release vector from T2.

- 9. The interrupt control logic sends the T2 the interrupt vector.

- 10. T2 passes the interrupt vector to CPUx the next time CPUx does the I/O read to the IVR.

- 11. CPUx handles the interrupt, and asserts SEOI when it has completed the task. See Section 3.2.3.3. The INT signal will de-assert during the SEOI.

- 12. T2 then allows the CIRQ<0> L line to follow INT. If another interrupt had become asserted during the interrupt handling process, INT will re-assert immediately following the SEOI.

#### 3.2.3.2 Interrupt priority

The 8259As are programmable. See Section 8.3.2 for more information.

#### 3.2.3.3 SEOI - Specific End of Interrupt

In the mode that Sable uses the 8259s, an SEOI command must be issued by the firmware twice. The cascaded interrupt controller requires the two SEOI commands,

#### 16 DIGITAL EQUIPMENT CORPORATION -

once for the master and once for the slaves. Since Sable is a multi-CPU system, the Specific End of Interrupt must be issued which includes as part of the command the IS level to be reset. See the 8259 specification for more information regarding programming.

#### 3.2.3.4 NMI

An NMI is an interrupt requiring immediate attention. The ESC generates NMI interrupts based upon various hardware and software events:

- 1. PCI PERR#

- 2. PCI SERR#

- 3. Add-In Board Parity Errors on the EISA expansion bus.

- 4. Fail-Safe Timer Timeout

- 5. EISA Bus Timeout

- 6. Software Generated NMI

All NMI sources can be enabled or disabled by individual enable/disable bits or by one NMI enable/disable bit. The ESC generates NMI directly to the T2 gate array. There is also an enable/disable bit in the T2. The T2 will assert CERR L if NMIs are enabled in the IOCSR and the ESC asserts the NMI signal.

## 3.3 T2 gate array

The T2 gate array is a 60K 299 pin ceramic PGA. It is a CBUS node which provides a bridge to a 32-bit PCI bus running at 33 MHz. The T2 is a fully compliant PCI bridge. All I/O, DMA and interrupt transactions to the 32-bit PCI bus occur through the T2 array. The T2 provides logic for translating and extending the CBUS address space into PCI address space. The address decode in the T2 is described in Chapter 5. It also provides read and write channels with an 8 entry TLB and read/write I/O channel.

#### 3.3.1 T2 Block diagram

T2 GATE ARRAY BLOCK DIAGRAM PS @95%

#### **18 DIGITAL EQUIPMENT CORPORATION -**

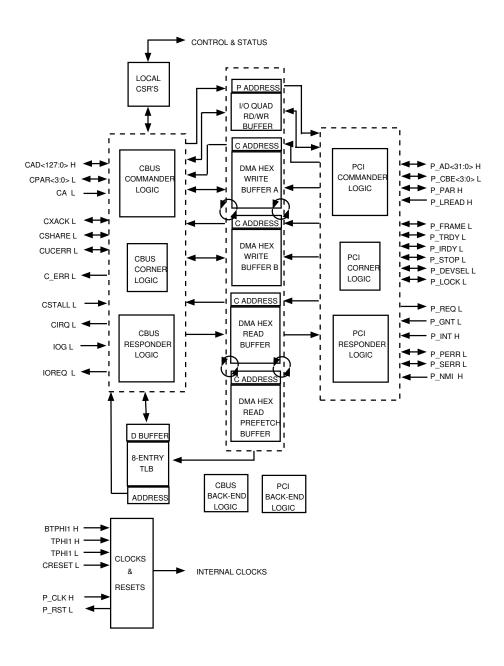

## 3.3.2 T2 Signals

## Figure 6: T2 Signals

T2\_PINOUT.DOC 100%

## 3.3.2.1 PCI Signals

## 3.3.2.1.1 P\_AD[31:0] H - Bidirectional, TTL, BD8TRP, 8ma

Address and Data are multiplexed on the same PCI pins. A bus transaction consists of an address phase followed by one or more data phases. PCI supports both read and write bursts. The address phase is the clock cycle in which P\_FRAME L is asserted. During the address phase P\_AD[31:0] H contain a physical address (32 bits). For I/O, this is a byte address; for configuration and memory it is a DWORD address. During data phases P\_AD[7:0] H contain the least significant byte (lsb) and P\_AD[31:24] H contain the most significant byte (msb). Write data is stable and valid when P\_IRDY L is asserted. Data is transferred during those cycles where both P\_IRDY L and P\_TRDY L are asserted.

## 3.3.2.1.2 P\_CBE[3:0] L - Bidirectional, TTL, BD8TRP, 8ma

Bus Command and Byte Enables are multiplexed on the same PCI pins. During the address phase of a transaction, P\_CBE[3:0] L define the bus command (refer to the PCI specification, Section 3.1 for bus command definitions). During the data phase, P\_CBE[3:0] L are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes carry meaningful data. P\_CBE[0] L applies to byte 0 (lsb) and P\_CBE[3] L applies to byte 3 (msb).

## 3.3.2.1.3 P\_PAR H - Bidirectional, TTL, BD8TRP, 8ma

Parity is even parity across P\_AD[31:0] H and P\_CBE[3:0] L. Parity generation is required by all PCI agents. P\_PAR H is stable and valid one clock after the address phase. For data phases, P\_PAR H is stable and valid one clock after either P\_IRDY L is asserted on a write transaction or P\_TRDY L is asserted on a read transaction. Once P\_PAR H is valid, it remains valid until one clock after the completion of the current data phase. (P\_PAR H has the same timing as P\_AD[31:0] but delayed by one clock). The master drives P\_PAR H for address and write data phases; the target drives P\_PAR H for read data phases.

## 3.3.2.1.4 P\_FRAME L - Bidirectional, TTL, BD8TRP, 8ma

Cycle Frame is driven by the current master to indicate the beginning and duration of an access. P\_FRAME L is asserted to indicate a bus transaction is beginning. While P\_FRAME L is asserted, data transfers continue. When P\_FRAME L is de-asserted, the transaction is in the final data phase.

## 3.3.2.1.5 P\_IRDY L - Bidirectional, TTL, BD8TRP, 8ma

Initiator Ready indicates the initiating agent's (bus master's) ability to complete the current data phase of the transaction. P\_IRDY L is used in conjunction with P\_TRDY L. A data phase is completed on any clock both P\_IRDY L and P\_TRDY L are sampled asserted. During a write, P\_IRDY L indicates that valid data is present on P\_AD[31:0] H. During a read, it indicates the master is prepared to accept data. Wait cycles are inserted until both P\_IRDY L and P\_TRDY L are asserted together.

#### 3.3.2.1.6 P\_TRDY L - Bidirectional, TTL, BD8TRP, 8ma

Target Ready indicates the target agent's (selected device's) ability to complete the current data phase of the transaction. P\_TRDY L is used in conjunction with P\_IRDY L. A data phase is completed on any clock cycle both P\_TRDY L and P\_IRDY L are sampled asserted. During a read, P\_TRDY L indicates that valid data is present on P\_AD[31:0] H. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted until both P\_IRDY L and P\_TRDY L are asserted together.

#### 3.3.2.1.7 P\_STOP L - Bidirectional, TTL, BD8TRP, 8ma

Stop indicates the current target is requesting the master to stop the current transaction.

#### 3.3.2.1.8 P\_LOCK L - Input, TTL

Lock indicates an atomic operation that may require multiple transactions to complete. When P\_LOCK L is asserted, non-exclusive transactions may proceed to an address that is not currently locked. A grant to start a transaction on PCI does not guarantee control of P\_LOCK L. Control of P\_LOCK L is obtained under its own protocol in conjunction with P\_GNT L. It is possible for different agents to use PCI while a single master retains ownership of P\_LOCK L. If a device implements Executable Memory, it must also implement P\_LOCK L and guarantee complete access exclusion in that memory. A target of an access that supports P\_LOCK L must provide exclusion to a minimum of 16 bytes (aligned). Host bridges that have system memory behind them must also implement P\_LOCK L.

#### 3.3.2.1.9 P\_DVSEL L - Bidirectional, TTL, BD8TRP, 8ma

Device Select, when actively driven, indicates the driving device has decoded its address as the target of the current access. As an input, P\_DVSEL L indicates whether any device on the bus has been selected.

#### 3.3.2.1.10 P\_REQ L - Output, BD8TRP, 8ma

Request indicates to the arbiter that this agent desires use of the bus. This is a point to point signal. Every master has its own P\_REQ L.

#### 3.3.2.1.11 P\_GNT L - Input, TTL

Grant indicates to the agent that access to the bus has been granted. This is a point to point signal. Every master has its own P\_GNT L.

## 3.3.2.1.12 P\_PERR L - Input, TTL

Parity Error is only for the reporting of data parity errors during all PCI transactions except a Special Cycle. The P\_PERR L is a sustained tri-state and must be driven active by the agent receiving data two clocks following the data when a data parity error is detected. The minimum duration of P\_PERR L is one clock for each data phase that a data parity error is detected. (If sequential data phases each have a data parity error, the P\_PERR L signal will be asserted for more than a single clock). P\_PERR L must be driven high for one clock before being tri-stated as with all sustained tri-state signals. There are no special conditions when a data parity error may be lost or when reporting of an error may be delayed. An agent cannot report a P\_PERR L until it has claimed the access by asserting P\_DVSEL L and completed a data phase.

## 3.3.2.1.13 P\_SERR L - Input, TTL

System Error is for reporting address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic. If an agent does not want a non-maskable interrupt (NMI) to be generated, a different reporting mechanism is required. P\_SERR L is pure open drain and is actively driven for a single PCI clock by the agent reporting the error. The assertion of P\_SERR L is synchronous to the clock and meets the setup and hold times of all bused signals. However, the restoring of P\_SERR L to the de-asserted state is accomplished by a weak pullup which is provided by the system designer and not by the signaling agent or central resource. This pullup may take two to three clock periods to fully restore P\_SERR L. The agent that reports P\_SERR L to the operating system does so anytime P\_SERR L is sampled asserted.

#### 3.3.2.1.14 P\_INT H - Input, TTL

P\_INT H is used by PCI devices to inform the operating system that an interrupting condition has occurred which requires servicing.

#### 3.3.2.1.15 P\_RST L - Output, BD4T, 4ma

Reset is used to bring PCI-specific registers, sequencers, and signals to a consistent state. Anytime P\_RST L is asserted, all PCI output signals must be driven to their benign state. In general, this means they must be tri-stated. P\_SERR L (open drain) is floated. P\_REQ L and P\_GNT L must both be tri-stated (they can not be driven low or high during reset). To prevent P\_AD, P\_CBE L and P\_PAR signals from floating during reset, the central device may drive these lines during reset (bus parking) but only to a logic low level. They may not be driven high. P\_RST L may be asynchronous to P\_CLK H when asserted or de-asserted. Although asynchronous, de-assertion is guaranteed to be a clean, bounce-free edge. Except for configuration accesses, only devices that are required to boot the system will respond after reset.

## 3.3.2.1.16 P\_CLK H - Input, TTL, 50% duty

Clock provides timing for all transactions on PCI and is an input to every PCI device. All other PCI signals, except P\_RST L are sampled on the rising edge of P\_CLK H, and all other timing parameters are defined with respect to this edge. PCI operates up to 33MHz, and in general, the minimum frequency is DC (0Hz).

### 3.3.2.1.17 P\_NMI H - Input, TTL

P\_NMI H is asserted by the PCI/EISA Bridge and indicates that a fatal condition has occurred.

## 3.3.2.1.18 P\_LREAD H - Input, TTL

LREAD H is an input into the T2 that provides an additional way for a PCI device to read more than one cache line (8 longwords). The PCI specification states that any PCI device wanting to read more than one cache line (16 longwords) should use either the Memory Read Line or Memory Read Multiple commands (Memory Read command is for one cache line). Some first pass PCI devices, however, were designed using only the Memory Read command, even though they possess the capabilities to read more than one cache line. Therefore, the LREAD H signal was implemented so that these devices could be allowed to read more than one cache line even though their command did not specify it. To operate correctly, LREAD H needs to be asserted during the address phase of the particular PCI devices read transaction. This signal is pulled up on the Motherboard.

#### 3.3.2.2 CBUS Signals

#### 3.3.2.2.1 CAD[127:0] H - Bidirectional, TTL, BD8TRP, 8ma

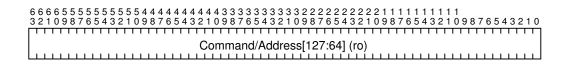

CAD[127:0] H are multiplexed between address and data information. Starting at cycle 0.5 to the end of cycle 1 CAD[127:0] H represent address, command, and commander identification information. For write cycles 2 and 3 and read cycle 5 and 6 they represent 128 bits of write or read data in each cycle, to complete a 256 bit data transfer. The command and address cycle is used by a commander to initiate a transaction. A commander shall drive the RESERVED fields high to ensure proper parity generation and to reduce switching noise. There are four types of transactions encoded by four command types: Write data, Read data, Exchanged read with write data, and the Null transaction. During write data cycles the commander drives data on CAD[127:0] H twice. The full 256 bits of data are written, since all memory and non-cachable address space write transactions are full hexaword. During Read Data Return and Read Data Error cycles the responder drives the data on CAD[127:0] H. A commander which does not receive acknowledgment to an initiated transaction aborts by completing the protocol in the specified number of transaction cycles. The commander is responsible for reporting this fault to the processor via a hard error interrupt.

## 3.3.2.2.2 CPAR[3:0] L - Bidirectional, TTL, BD8TRP, 8ma

CPAR[3:0] L is computed over each longword of the 128-bit CAD[127:0] H. Odd parity is used, where the "exclusive OR" of all bits including the parity bit is a "0". Good parity is defined as all bits, including the parity bit, have an odd number of true values. When the bus is idle, the backplane ensures that the bus defaults to a pulled up level. The 33 high levels cause incorrect parity to be guaranteed on an idle bus. If a device is granted the bus but chooses not to use it during a given cycle, it is responsible for driving the CAD[127:0] H to valid levels and CPAR[3:0] L with correct parity.

## 3.3.2.2.3 CXACK L - Bidirectional, TTL, BD8TRP, 8ma

In response to each address and command cycle, a responder is required to acknowledge it had received the command and address with good parity by asserting CXACK\_ L two cycles after cycle 1, regardless of the CSTALL L state. This could be cycle 2 or cycle 3. A bystander must check parity for all address and command cycles, and if an error is detected, log the error and notify a CPU via the C\_ERR\_L interrupt. Bystanders should not check data parity. Responders must also acknowledge the reception of write data with good parity, by asserting CXACK L two cycles after the write data is received. That is in cycle 4 and cycle 5 in no CSTALL L assertion, or in the multiple cycle 4(s) if CSTALL L is asserted. A responder which accepts writes to non-cachable space registers should check octaword parity and if the first received octaword has a detected data parity error the write shall not be completed to the accessed register. CXACK L is NOT used for flow control. Commanders must check for the CXACK L response and complete the transaction cycle flow. If CX-ACK L assertion is not detected in the correct cycles, the commander completes the transaction, logs the failing event(s) and posts a C ERR L interrupt. Address and command cycles to non-decoded address spaces are cycled through the transaction by the commander without acknowledgment.

## 3.3.2.2.4 BTPHI1 H, TPHI1 H - Input, TTL, 50% Duty

BTPHI1 provides timing for all transactions on CBUS and is an input to every CBUS interface. CBUS operates at 41.67 MHz with a 24ns cycle time.

## 3.3.2.2.5 TPHI1 L - Input, TTL, 50% Duty

TPHI1 L is an inverted version of TPHI1 H.

## 3.3.2.2.6 CSHARED L - Output, BD24TRP, 24ma

Based on the shared state of the cache block, the commander determines whether to do a write-through when the contents of the memory block are written. CSHARED L is asserted from cycle 3.5 to 4.5 by a CPU or I/O bystander that contains the referenced valid memory block during any transaction to be sampled at the end of cycle 4.5. CDIRTY L shall not assert during non-cachable address space transactions. CSHARED L could change state in cycles 2 and 5. Drivers must not be enabled in

#### 24 DIGITAL EQUIPMENT CORPORATION -

cycle 0. In addition, a CPU node must respond with shared status for a CBUS read of a cache block which has a valid lock address and lock flag. Any CPU node may assert CSHARED L as the I/O node performs a transaction. During a write transaction, the bystander CPU snoop result may assert CSHARED L to signal that it accepted the write, and the commander must retain the shared state of the block. Alternatively, the bystander CPU must not assert the CSHARED L signal if it invalidates the cache block. Hence, CPU nodes can either accept and update writes or invalidate on writes. An I/O node monitors transaction addresses and returns CSHARED L status for read transactions to a block it has buffered for merging with write data. For write transactions from another node to an I/O node buffered block, the block is invalidated, and read again, to obtain the most recent copy. This enables the I/O node to merge write data to a block which a CPU node may be polling.

#### 3.3.2.2.7 CUCERR L - Input, TTL

Per transaction unrecoverable data errors are reported via the CUCERR L signal. For read transactions CUCERR\_L asserts in cycle 5 or 6 with the octaword of bad data. For write transactions CUCERR L asserts in cycle 2 or 3 with the octaword of bad data. Also, CUCERR L is used for flow control of store conditional writes to the non-cachable address space mailbox pointer register and shall assert in the first cycle 4 to be sampled by the commander at the end of the first cycle 4. The I/O responder may sustain the assertion of CUCERR L during multiple cycle 4s, but shall negate CUCERR L no later than the end of the last cycle 4. CUCERR L is sampled by the commander to signify data errors at the end of cycle 5 or 6 for reads, and to signify STxC non-cachable address space write failures at the end of the first cycle 4. The responder samples CUCERR L to check the validity of the written data at the end of cycles 2 or 3 for writes. CUCERR L shall assert with each read data return cycle or write data cycle which has uncorrectable data. The responder node which asserts CUCERR L in cycle 5 shall leave the signal asserted through cycle 6. The commander node which asserts CUCERR L in cycle 2 shall leave the signal asserted through cycle 3. The CPU nodes must know which octaword of data is bad as it is received to signal the ALPHA AXP chip correctly. The memory controller specification is to always assert CUCERR L for uncorrectable errors during read data return cycles 5 and 6.

#### 3.3.2.2.8 CA L - Input, TTL

CA L is driven only by the CBUS arbiter located on the CPU0 node. Nodes receive CA L to identify cycle 0 as the start of a new transaction. The address and command must be driven by the granted commander in cycle 1, following cycle 0. There are cases where the next arbitration grant, which defines the next CA L assertion, overlap the last cycle of a transaction, however tri-state overlap is ensured to be avoided by the transaction timing.

## 3.3.2.2.9 IOG L - Input, TTL

IOG L asserts on a NOT TPHI1 edge. 0.5 cycle before cycle 0, 1 cycle after it was sampled, to grant the CBUS to the requesting I/O node. The arbiter asserts CA L in cycle 0, and the I/O node shall drive the address in cycle 1. IOG L may negate on the NOT TPHI1 clock after cycle 0, to be sampled 1 cycle later. IOG L is a unidirectional signal driven from CPU0 to the I/O nodes. An I/O node is guaranteed exclusive use of CBUS as long as the IOREQ L is held asserted, otherwise fair arbitration is assumed.

## 3.3.2.2.10 CRESET L - Input, TTL

This signal returns the system to an initial state when asserted by asynchronously forcing each node to disable its bus drivers. During a power-up, CRESET L remains asserted until backplane +5v and CPU +3.3v power are stable, CBUS oscillators are running at full harmonic content and voltage swing. These conditions are ANDed with the ASYNC\_RESET L signal from the power-controller, synchronized to the TPHI1 clock to negate CRESET L synchronous to TPHI1. Nodes shall have 4nS minimum setup time of the negation of CRESET L to their TPHI1 clock edge. CRE-SET L may assert after the system has powered-up for a minimum of 10mS to force all CBUS nodes to an initial state. CRESET L shall assert 100nS maximum after the assertion of ASYNC\_RESET L.

## 3.3.2.2.11 IOREQ L - Output, BD8T, 8ma

## 3.3.2.3 IOREQ\_L, XIOREQ\_L

Integral and expansion I/O nodes assert IOREQ L on any NOT TPHI1 clock edge to request the CBUS. IOREQ L is a unidirectional signal to the CPU0 module. These signals are sampled by a NOT TPHI1 edge 1 cycle before IOG L is asserted on a NOT TPHI1 edge. Once asserted, IOREQ L shall not negate before cycle 0.5 after IOG L has asserted. IOREQ L may be held asserted, and then IOG L could assert in the next arbitration cycle or the second arbitration cycle. An I/O node may retain commander status of the CBUS by leaving the request asserted. The I/O commander may signal the arbitrer to search for another node to grant by negating the request for 1 cycle between cycles 0 and 4.

#### 3.3.2.3.1 CIRQ L - Output, BD8T, 8ma

This level sensitive interrupt request signal asserts asynchronously from the I/O node to all CPU nodes. It is a general device level interrupt. System software can decide which CPU node is responsible for servicing this signal.

#### NOTE

The CIRQ L signal can be shared by CPU nodes, the interrupt controllers have a contention prevention mechanism for passive release.

## 3.3.2.3.2 CSTALL L - Input, TTL

CBUS transactions can be stalled an integral number of cycles by writing or exchanging commanders to memory address space in cycle 2 or by responders or bystanders in cycle 4 by asserting CSTALL L in cycle 1.5 or cycle 3.5. Commander driven stalls in cycle 2, with CSTALL L driven not later than cycle 1.5, allow a cached node to read data from the cache, merge it with processor write data, and then continue the write to memory. Stall shall not be asserted by a responder or bystander node later than cycle 3.5. A bystanding node shall not stall any non-cachable address space reference. This provides per transaction flow control. The negation in cycle 2.5 or 4.5 enables entry to cycle 3 or 5, 1.5 cycle later to continue a transaction. Arbitration request signals may assert during stalled cycles. There are two copies of this signal, each shall be driven by a single stub per node. Since the bus interface chips are QW sliced, one copy is for the even slice and the other copy is for the odd slice. It is possible for the even and odd CPU interface chips to become 1.5 cycles out of synchronization, if the snoop result differs due to faulty hardware. A recovery procedure that involves having the two slices communicate via an open drain bidirectional voted signal at the end of a transaction allows re-synchronization. Designers discretion is expected concerning permissible numbers of stalled cycles per transaction. However, due to the overall performance and I/O latency impact, stalling beyond 6 cycles, as a general design practice is not permitted. A timer shall not be implemented to enforce this policy.

## 3.3.2.3.3 C\_ERR L - Output, BD24TRP, 24ma

This synchronous signal is asserted in cycle 0 by a CPU node or cycles 0 or 1 by an I/O or memory node of a transaction, or whenever the CBUS is idle, for a maximum of one cycle. The signal is sampled to cause an interrupt to all processor nodes. This interrupt is asynchronous to a CBUS transaction that may have caused an error. This signal indicates a hard or soft error or a latent error to a CPU from a CPU, memory, or an I/O node. A node shall provide a soft error interrupt enable method in its CSRs if it is a source of soft errors. Latent errors are defined as being reported to the CPU nodes after the associated CBUS transaction has completed. During CPU commander transactions to secondary I/O space, the PCI Bridge chip or the expansion I/O interface may assert C\_ERR L on the cycle 3 TPHI1 edge for one and only one cycle, and negate C\_ERR L on the cycle 4 TPHI1 edge. This signals a retry to the commanding CPU node. A commander implementing this simple retry signaling mechanism does not implement a limit counter. The responder node is obligated to abort the commander should an exception occur.

#### 3.3.2.3.4 MBA<7:0> H - Bidirectional, TTL, BD2T, 2ma

These general purpose lines are used to multiplex out T2 internal state machine state bits for testing purposes. Additionally, these signals can be connected to external logic requiring storage of certain error or status conditions.

#### 3.3.2.3.5 PARAMOUT - Output, B4, 4ma

A signal used for testing.

#### 3.3.2.3.6 TRIST L - Input, TTL

A signal used to tri-state all T2 output or bidirectional signals simultaneously.

#### 3.3.3 T2 Functionality

#### 3.3.3.1 CBUS transactions

The T2 ASIC can operate as both a Master and Slave on the CBUS. It supports the following following CPU initiated transactions:

- **LDx\_L to I/O Space** This is reflected as a CBUS read operation to I/O space. The T2 retries this transaction until the data is read from the target device. Once the data is in the T2 array, all further DMA write traffic on the PCI is retried until the CPU has read the data successfully. This transaction has no effect on the lock flag.

- **STx\_C to I/O Space** Write to I/O space are treated as "dump and run" writes. There is a single quadword write buffer for I/O transactions. Subsequent writes are retried until the PCI write transaction is complete and the buffer is free.

- **Read/Write Clock to Local CSR space** These cycles are complete in a single CBUS cycle.

#### 3.3.3.2 PCI transactions

The T2 supports the following PCI transactions:

- Acting as a PCI Master:

- I/O Read This is the PCI transaction done in response to a LDx\_L from the processor to Sparse I/O space. The T2 supports byte, word, tribyte, longword and quadword lengths.

- I/O Write This is the PCI transaction done in response to a STx\_C from the processor to Sparse I/O space. The T2 supports byte, word, tribyte, longword and quadword lengths.

- Configuration Reads and Writes This is the PCI transaction done in response to a LDx\_L or STx\_C from the processor to Configuration Space. The T2 supports byte, word, tribyte, longword and quadword lengths. Both type 0 and type 1 are supported.

- Memory Read This is a PCI transaction done in response to LDx from the processor to either Sparse Memory space or Dense Memory space. In Sparse Memory space the T2 supports byte, word, tribyte, longword and quadword lengths. In Dense Memory Space the T2 supports quadword only.

- Memory Write This is a PCI transaction done in response to STx from the processor to either Sparse Memory space or Dense Memory space. In Sparse Memory space the T2 supports byte, word, tribyte, longword and quadword lengths. In Dense Memory Space the T2 supports lengths ranging from longword to hexaword in longword increments.

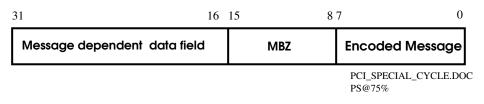

- Special Cycle Special cycles are initiated by a CPU write to a local T2 CSR. Refer to the Addressing Chapter, Chapter 5, and the PCI specification for more details on Special Cycles.

- Acting as a PCI Target:

- **Memory Read DMA** The T2 contains a hexaword DMA read buffer with an enabled hexaword read prefetch buffer to support byte to burst length PCI transfers into system memory from some PCI device. When the read prefetch buffer is disabled, the maximum burst transfer size accepted by the T2 is a single hexaword. When the read prefetch buffer is enabled, there is no maximum burst transfer size restriction, although it is expected that each PCI Master use a fair time slice of the PCI as to not degrade overall system performance. There are two types of DMA transactions supported by the T2, direct mapped and scatter/gather mapped.

- Memory Write DMA The T2 contains two hexaword DMA write buffers with two modes of operation to support byte to burst length PCI transfers into system memory from some PCI device. When the write buffers are in single DMA mode, each buffer functions individually and allows a maximum burst transfer size of a single hexaword. When the write buffers are in multiple DMA mode, both buffers can be used for a single DMA transaction. There is no maximum burst transfer size restriction in multiple DMA mode, although it is expected that each PCI Master use a fair time slice of the PCI as to not degrade overall system performance. There are two types of DMA transactions supported by the T2, direct mapped and scatter/gather mapped.

#### 3.3.3.3 Translation Look-aside Buffer (TLB)

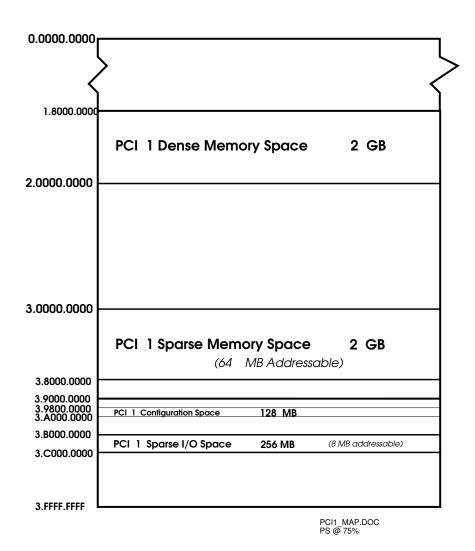

To improve performance during scatter/gather mapped DMA transactions, the T2 contains an eight entry TLB. The TLB allows the T2 to cache up to eight Page Frame Numbers (PFN's) from a page table stored in system memory. If the TLB were disabled, each scatter/gather DMA transaction would require the T2 to read the associated PFN directly from system memory. The TLB can be enabled from the T2's IOCSR. Replacement of PFN's in the TLB logic that allow all resident entries to be invalidated, if necessary. However, the TLB also keeps track of any PFN modified in the System memory resident page table by a CPU and will invalidate entries on an individual basis if a page table PFN it contains is modified. The contents of the TLB is readable through T2 CSR registers.

#### 3.4 Standard I/O Module

See Chapter 8 for a complete description of the Standard I/O module.

# **CHAPTER 4**

## CONTROL STATUS REGISTERS

Several types of CSRs exist in the Sable I/O subsystem. The first type are the CBUS CSRs. These are only accessible from the CBUS (System bus) and contain some required system registers. The only CBUS CSRs in the Sable I/O subsystem are found in the T2 gate array.

The second type of CSRs are found in PCI configuration space. They are accessed by the system through a certain address range and converted by the T2 gate array to Configuration cycles on the PCI. Configuration space is intended for configuration, initialization and catastrophic error handling functions. Its use should be restricted to initialization software and error handling software. All operational software must use I/O and/or memory space accesses to manipulate device registers.

The third type of CSRs are the device specific CSRs. These are found in PCI0 memory or I/O space. The address tables for the TULIP, NCR 53C810 and ESC/PCEB registers are found in this chapter. Descriptions of these CSRs can be found in their individual specifications.

#### 4.1 CBUS CSRS

All the CBUS CSRs in the Sable I/O subsystem are in the T2 gate array. The CBUS CSRs in the T2 are all aligned on hexaword boundaries and have quadword length. The T2 contains the three standard CBUS registers, CSR0, CSR1 and CSR2. The contents of CSR1 and CSR2 are only valid when an error bit is set in CSR0.

#### 4.1.1 T2 CBUS registers

| Register Name                     | Mnemonic | EV Address  | Length     | Attributes              |

|-----------------------------------|----------|-------------|------------|-------------------------|

| I/O Control/Status Register       | IOCSR    | 3.8E00.0000 | 8 bytes    | R/W                     |

| CBUS Error Register 1             | CERR1    | 3.8E00.0020 | 8 bytes    | R/W                     |

| CBUS Error Register 2             | CERR2    | 3.8E00.0040 | 8 bytes    | RO                      |

| CBUS Error Register 3             | CERR3    | 3.8E00.0060 | 8 bytes    | RO                      |

| PCI Error Register 1              | PERR1    | 3.8E00.0080 | 8 bytes    | R/W                     |

| PCI Error Register 2              | PERR2    | 3.8E00.00A0 | 8 bytes    | RO                      |

| PCI Special Cycle Register        | PSCR     | 3.8E00.00C0 | 8 bytes    | Write Only <sup>1</sup> |

| High Address Extension Register 1 | HAE0_1   | 3.8E00.00E0 | 8 bytes    | R/W                     |

| High Address Extension Register 2 | HAE0_2   | 3.8E00.0100 | 8 bytes    | R/W                     |